# HVV1012-060

60 Watts, 50V, 1025-1500MHz, 10μs, 1% Duty Cycle

## **DESCRIPTION**

The high power HVV1012-060 device is a high voltage silicon enhancement mode RF transistor designed for L-Band pulsed avionics applications operating over the frequency range from 1025MHz to 1150MHz.

#### **FEATURES**

High Power Gain Excellent Ruggedness 48V Supply Voltage

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol         | Parameter Value      |        | Unit |

|----------------|----------------------|--------|------|

| $V_{DSS}$      | Drain-Source Voltage | 95     | V    |

| $V_{GS}$       | Gate-Source Voltage  | 10     | V    |

| $I_{DSX}$      | Drain Current        | 4      | Α    |

| $P_D^2$        | Power Dissipation    | 625    | W    |

| T <sub>S</sub> | Storage Temperature  | -65 to | °C   |

|                |                      | +200   |      |

| T <sub>J</sub> | Junction             | 200    | °C   |

|                | Temperature          |        |      |

# THERMAL CHARACTERISTICS

| Symbol            | Parameter          | Max  | Unit |

|-------------------|--------------------|------|------|

| $\theta_{JC}^{1}$ | Thermal Resistance | 0.28 | °C/W |

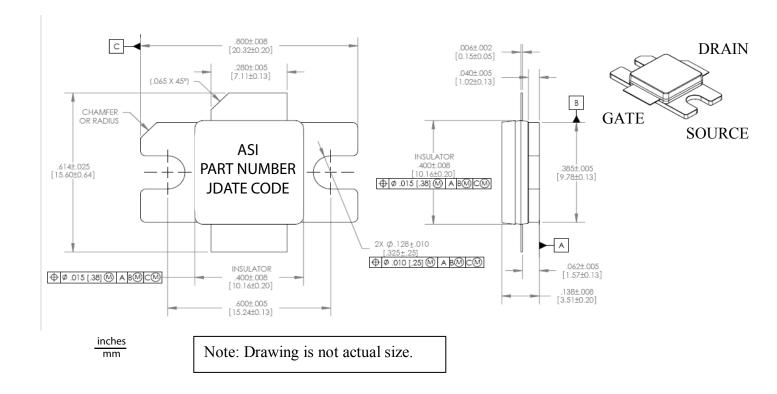

# **PACKAGE**

The device resides in a two-lead metal flanged package with liquid crystal polymer lid. The HV400 package style is qualified for gross leak test – MIL-STD-883, Method 1014.

#### **RUGGEDNESS**

The HVV1012-060 device is capable of withstanding an output load mismatch corresponding to a 20:1 VSWR at rated output power and operating voltage across thefrequency band of operation.

| Symb             | ol Parameter          | Test Condition  | Max  | Units |

|------------------|-----------------------|-----------------|------|-------|

| LMT <sup>1</sup> | Load                  | $P_{OUT} = 60W$ | 20:1 | VSWR  |

|                  | Mismatch<br>Tolerance | F = 1150MHz     |      |       |

## **ELECTRICAL CHARACTERISTICS**

| Symbol           | Parameter              | Conditions                           | Тур  | Units |

|------------------|------------------------|--------------------------------------|------|-------|

| $V_{BR(DSS)}$    | Drain-Source Breakdown | VGS=0V,ID=2mA                        | 102  | V     |

| I <sub>DSS</sub> | Drain Leakage Current  | VGS=0V,VDS=48V                       | <50  | μA    |

| $I_{GSS}$        | Gate Leakage Current   | VGS=5V,VDS=0V                        | <1   | μA    |

| $G_P^1$          | Power Gain             | P <sub>OUT</sub> =60W,F=1025,1150MHz | 23   | dB    |

| $IRL^1$          | Input Return Loss      | P <sub>OUT</sub> =60W,F=1025,1150MHz | 9    | dB    |

| $\eta_{D}^{-1}$  | Drain Efficiency       | P <sub>OUT</sub> =60W,F=1025,1150MHz | 52   | %     |

| $PD^1$           | Pulse Droop            | P <sub>OUT</sub> =60W,F=1025,1150MHz | <0.3 | dB    |

$^{1}$ Under Pulse Conditions: Pulse Width =  $10\mu$ sec, Pulse Duty Cycle = 1% at VDD = 48V, IDQ = 25mA  $^{2}$ Rated at  $T_{CASE} = 25^{\circ}$

REV. A

ASI Semiconductor, Inc. (ASI) reserves the right to make changes to information published in this document at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof. Information in this document is believed to be accurate and reliable. However, ASI does not give any representations or warranties, either express or implied, as to the accuracy or completeness of such information and shall have no liability no liability for consequences resulting from the use of such information. No license, either expressed or implied, is conveyed under any ASI intellectual property rights, including any patent rights.